### Overview

V4220M is a high performance audio codec IC using delta-sigma ADC and DAC techniques, its applications include digital effects processors, DAT, and multitrack recorders.

#### Its **features** are:

- ◆ 100dB dynamic range A/D converters

- ◆ 100dB dynamic range D/A converters

- ◆ 105dB DAC signal-to-noise ratio

- ◆ Analog Volume Control

- ◆ Differential inputs / outputs

- On-chip Anti-aliasing and Output Smoothing Filters

- ◆ Selectable De-emphasis Filters for 32k, 44.1k and 48kHz sample rates

- ◆ Package: SSOP28

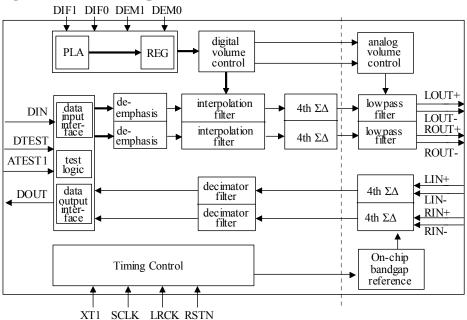

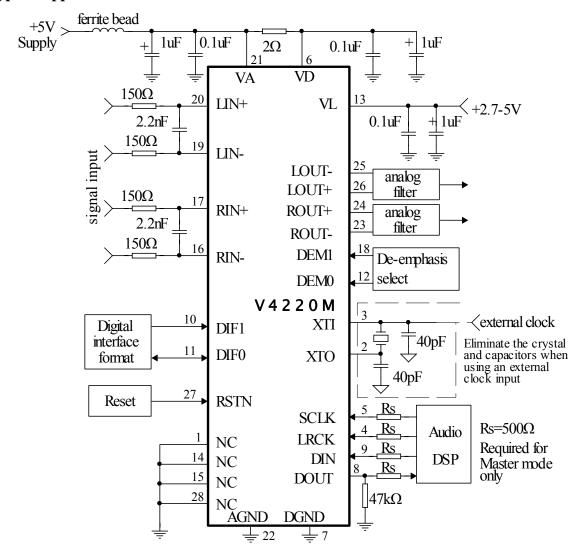

### **Block Diagram and Pin Description**

### **Function Description**

V4220M is a high performance, 24-bit, stereo, audio codec IC that includes two channel ADC and two channel DAC. The fourth-order delta-sigma A/D converters the analog input to the 24bit serial outputs; the delta-sigma DAC includes the interpolation filter, noise shaping modulator and low-pass smoothing filter.

The V4220M also includes a digital selectable de-emphasis filter for 32k, 44.1k and 48k Hz sample rates; an analog volume control architecture can make an 113.5dB attenuation in 0.5dB steps, which preserves dynamic range during attenuation. The V4220M provides a serial interface to read/write the internal registers.

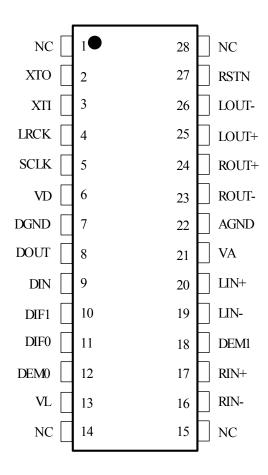

# **Pin Configuration**

# Pin Description and Structure Scheme

| Pin | Symbol          | Function                 | Attribute | Structure Scheme                       |

|-----|-----------------|--------------------------|-----------|----------------------------------------|

| 1   | NC              | /                        | /         | /                                      |

| 2   | ХТО             |                          | I/O       | ************************************** |

| 3   | XTI             | OSC Input/output         | I/O       |                                        |

| 4   | LRCK            | Left/right clock         | I/O       | - 15                                   |

| 5   | SCLK            | Serial data clock        | I/O       |                                        |

| 6   | VD              | Digital power            |           |                                        |

| 7   | DGND            | Digital ground           |           |                                        |

| 8   | DOUT            | Serial data output       | I/O       | 4.7                                    |

| 9   | DIN             | Serial data input        | I/O       | <b>→</b> 9  <b>3</b>                   |

| 10  | DIF1 (scl/cclk) | Digital interface format | I         | <b>←</b>                               |

| 11    | DIF0 (sda/cdin)            |                       | I/O | -1G      |

|-------|----------------------------|-----------------------|-----|----------|

| 12    | DEM0(ad0/cs)               | De-emphasis select    | I   |          |

| 18    | DEM1(I <sup>2</sup> C/SPI) | De-emphasis select    | 1   | ÷        |

| 13    | VL                         | Digital logic power   |     |          |

| 14,15 | NC                         | /                     | /   |          |

| 16    | RIN-                       | Differential right    | ī   | disable➤ |

| 17    | RIN+                       | channel analog input  | 1   |          |

| 19    | LIN-                       | Differential left     | т   |          |

| 20    | LIN+                       | channel analog input  | 1   | enable > |

| 21    | VA                         | Analog power          |     |          |

| 22    | AGND                       | Analog ground         |     |          |

| 23    | ROUT-                      | Differential right    | I/O |          |

| 24    | ROUT+                      | channel analog output | 1/0 | + \      |

| 25    | LOUT+                      | Differential left     | I/O | + ~~     |

| 26    | LOUT-                      | channel analog output | 1/0 |          |

| 27    | RSTN                       | Reset                 | I   |          |

| 28    | NC                         | /                     | /   |          |

# **Electrical Characteristics**

# Absolute Maximum Ratings

Unless otherwise specified,  $T_{amb}=25^{\circ}C$

| Parameter             | Symbol           | Value            | Unit                 |

|-----------------------|------------------|------------------|----------------------|

| Power Supplies        | $V_A, V_D, V_L$  | -0.3~6           | V                    |

| Power Supply Current  | $I_{all}$        | 90               | mA                   |

| Power Dissipation     | $P_{\mathrm{D}}$ | 450              | mW                   |

| Operating Temperature | $T_{amb}$        | -40~85           | $^{\circ}\mathbb{C}$ |

| Storage Temperature   | $T_{stg}$        | <b>-</b> 65∼+150 | $^{\circ}$ C         |

# Recommended Operating Conditions

| Parameter     | Cymbol |      | Unit |      |      |  |

|---------------|--------|------|------|------|------|--|

| Parameter     | Symbol | Min  | Тур  | Max  | Oill |  |

| Digital power | VD     | 4.75 | 5.0  | 5.25 | V    |  |

| Analog power  | VA     | 4.75 | 5.0  | 5.25 | V    |  |

| Digital power | VL     | 2.7  | 5.0  | 5.25 | V    |  |

### • Electrical Characteristics

Unless otherwise specified,  $T_{amb}\!\!=\!25\,^{\circ}\!\!\mathrm{C}$  ,  $V_{A}\!\!=\!\!V_{D}\!\!=\!\!5V$

| Parameter                        | Symbol                        | Test Conditions                 |       | Specifications Min Typ max |        |      |

|----------------------------------|-------------------------------|---------------------------------|-------|----------------------------|--------|------|

| 1 arameter Symi                  |                               | /Comments                       |       | Тур                        | max    | Unit |

| DC Parameter                     |                               |                                 |       |                            |        |      |

| Power supply Current             |                               |                                 |       |                            |        |      |

| VA                               | Iva                           | $V_L=5V$                        |       | 46                         | 60     | mA   |

| VD                               | Ivd                           | $V_L=5V$                        |       | 9                          | 20     | mA   |

| VL                               | Ivl                           | $V_L=5V$                        |       | 3                          | 5      | mA   |

|                                  | 1                             | Analog input characteris        | stics |                            |        |      |

| Total harmonic distortion        | THD                           |                                 |       | 0.003                      |        | %    |

| ADC dynamic range                |                               |                                 | 92    | 100                        | -      | dB   |

| Total harmonic distortion +noise | THD+N                         | Note 1                          |       | -92                        | -87    | dB   |

| Full scale input voltage         |                               | Differential                    |       | 2.0                        | 2.1    | Vrms |

|                                  | Analog output characteristics |                                 |       |                            |        |      |

| Total harmonic distortion        | THD                           |                                 |       | 0.003                      |        | %    |

| DAC dynamic range                |                               |                                 | 92    | 100                        | -      | dB   |

| DAC SNR                          | SNR                           |                                 | 97    | 105                        |        | dB   |

| Attenuation step size            |                               |                                 | 0.35  | 0.5                        | 0.65   | dB   |

| Common mode output voltage       |                               |                                 |       | 2.4                        |        | V    |

|                                  |                               | Digital characteristics         | 5     |                            |        |      |

| High-level input voltage         | Vih                           | VL=5V                           | 2.8   |                            | VL+0.3 | V    |

| Trigii-level iliput voltage      | Vil                           | VL=3V                           | 2.0   |                            | VL+0.3 | V    |

| Low-level input voltage          | Vil                           |                                 | -0.3  |                            | 0.8    | V    |

| High-level output voltage        |                               |                                 | VI-1  |                            |        | V    |

| Low-level out voltage            |                               |                                 |       |                            | 0.5    | V    |

| Input leakage current            |                               | Logic Inputs                    |       |                            | 10     | μΑ   |

| Output leakage current           |                               | High Impedance<br>Logic Outputs |       |                            | 10     | μА   |

Note 1: referenced to typical full-scale differential input voltage(2 Vrms)

### **Test Circuit**

### • DC Test Circuit

### • AC Test Circuit

Page 5 of 10

### **Characteristics Curve**

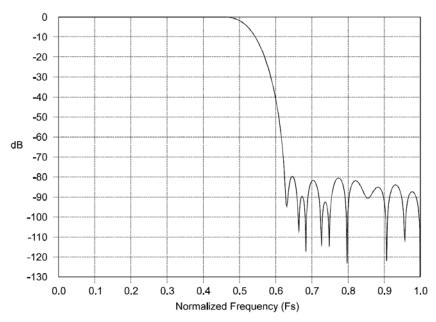

ADC Filter Response

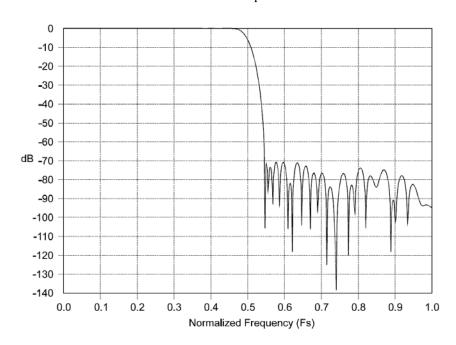

DAC Filter Response

# **Timing Sequence and Port Operating Description**

### • digital interface format

| DIF1 DIF0   | Digital Interface Format (Input)              |

|-------------|-----------------------------------------------|

| 00(default) | Format 1: I <sup>2</sup> S, up to 24-bit data |

| 01          | Format 2: Left justified, up to 24-bit data   |

| 10          | Format 3: Right justified, 24-bit Data        |

| 11          | Format 4: Right justified, 20-bit Data        |

Page 6 of 10

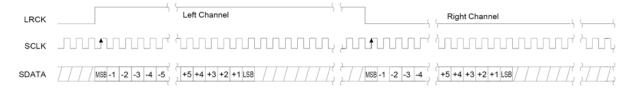

#### Serial data format 00:

| LRCK  | Left Channel                                              | Right Channel                                |

|-------|-----------------------------------------------------------|----------------------------------------------|

| SCLK  | nn, hummy, humm                                           | uu, mumuu, mi                                |

| SDATA | / / MSB -1 -2 -3 -4 -5 / +5 +4 +3 +2 +1 LSB / / / / / MSB | -1  -2  -3  -4       +5  +4  +3  +2  +1  LSB |

| Master                              | Slave                      |

|-------------------------------------|----------------------------|

| I <sup>2</sup> S, up to 24-bit data | $I^2S$ , up to 24-bit data |

| XTI=256,384,512Fs                   | XTI=256,384,512Fs          |

| LRCK=4 to 50kHz                     | LRCK=4 to 50kHz            |

| SCLK=64Fs                           | SCLK=48,64,128Fs           |

#### Serial data format 01:

| Master                            | Slave                             |

|-----------------------------------|-----------------------------------|

| Left-justified, up to 24-bit data | Left-justified, up to 24-bit data |

| XTI=256,384,512Fs                 | XTI=256,384,512Fs                 |

| LRCK=4 to 50kHz                   | LRCK=4 to 50kHz                   |

| SCLK=64Fs                         | SCLK=48,64,128Fs                  |

### Serial data format 10:

| Master                       | Slave                        |

|------------------------------|------------------------------|

| Right-justified, 24-bit data | Right-justified, 24-bit data |

| XTI=256,384,512Fs            | XTI=256,384,512Fs            |

| LRCK=4 to 50kHz              | LRCK=4 to 50Hz               |

| SCLK=64Fs                    | SCLK=64Fs                    |

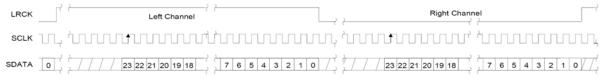

#### Serial data format 11:

| LRCK  | Left Channel                                              | L, | Right Channel                                        | ? |

|-------|-----------------------------------------------------------|----|------------------------------------------------------|---|

| SCLK  | uuuuuuuuuuuuuuu, $u$                                      | T, |                                                      | ç |

| SDATA | 1 0 7 7 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | Ę  | 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 // | ۲ |

| Master                       | Slave                        |

|------------------------------|------------------------------|

| Right-justified, 20-bit data | Right-justified, 20-bit data |

| XTI=256,384,512Fs            | XTI=256,384,512Fs            |

| LRCK=4 to 50kHz              | LRCK=4 to 50Hz               |

| SCLK=64Fs                    | SCLK=64Fs                    |

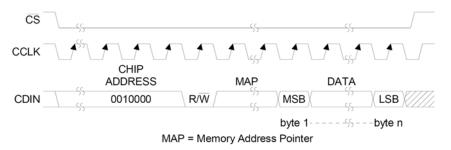

#### Control port timing

#### SPI mode

In SPI mode, CS is the V4220M chip select signal, CCLK is the control port bit clock, CDIN is the input data line from the micro controller and the chip address is 0010000, all the signal are input and data is clocked in on the rising edge of CCLK.

Figure behind shows the operation of the control port in SPI mode. To write to a register, bring CS low. The first 7 bits on CDIN form the chip address, and must be 001000. The eighth bit is a read/write indicator, which must be low to write. Register reading from the V4220M is not supported in SPI model The next 8 bits form the Memory address Pointer(MAP), which is set to the address of the register that is to be updated. The next 8 bits are the data which will be placed into a register designated by the MAP.

The V4220M has a MAP auto increment capability, enabled by he INCR bit in the MAP register. If INCR is a zero, then MAP will stay constant for successive writes. If INCR is set to a 1, then MAP will auto increment after each byte is written, allowing block writes of successive registers. Register reading from V4220M is not supported in the SPI mode.

#### • I<sup>2</sup>C mode

In I<sup>2</sup>C mode, SDA is a bi-directional data line. Data is clocked into and out of the part by the clock, SCL, with the clock to data relationship as shown in the following figure. There is no CS pin. Pin ad0 form s the partial chip address and should be tied to VDD or DGND as desired. The upper 6 bits of the 7 bit address field must be 001000. In order to communicate with the V4220M, the LSB of the chip address field(first byte sent to the V4220M)should match the setting of the ad0 pin. The eighth bit of the address byte is the read/write bit(high for a read, low for a write). If the operation is a write, the next byte is the memory address pointer which selects the register to be read/write. If the operation is a read, the contents of the register pointed to by the memory address pointer will be output. Setting the auto increment bit in MAP, allows successive reads or writes of consecutive registers. Each byte is separated by an acknowledge bit.

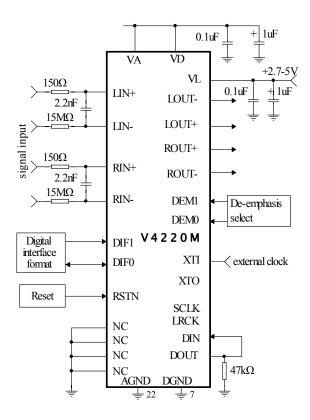

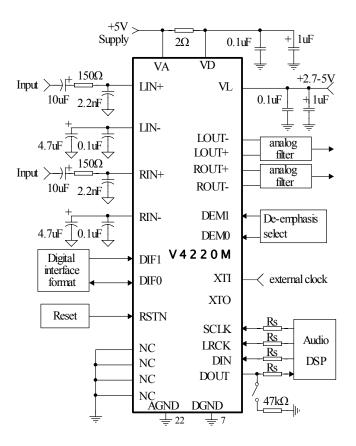

## **Typical Application Circuit and Information**

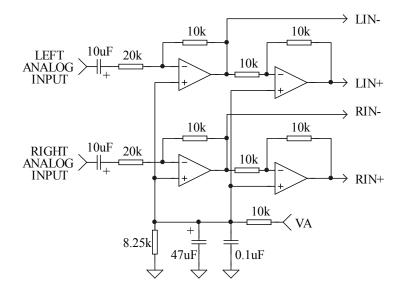

### • Input buffer

**Optional Input Buffer**

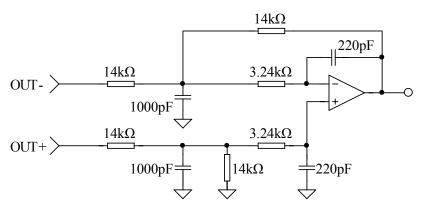

### Output buffer

2-pole Butterworth Filter

### Applications Information

Master mode and slave mode:

The V4220M may be operated in either master mode or slave mode. In master mode, SCLK and LRCK are outputs which generated by inner circuit. The V4220M will operate in master mode when a  $47k\Omega$  pulldown resistor is present on DOUT at startup or after reset, see application circuit. LRCK and SCLK are inputs to the V4220M when operating in slave mode, see the available clocking modes.